- #What to do if quartus ii can't pick up my usb blaster drivers#

- #What to do if quartus ii can't pick up my usb blaster driver#

- #What to do if quartus ii can't pick up my usb blaster software#

Signal connected to the BUSY pin of the ADAS3022 Signal connected to the SDO pin of the ADAS3022 The value of the CPHA bit in the ADAS configuration register The value of the CMS bit in the ADAS configuration register Signals that the write from CED1Z_interface module has been performed Signals that at port DATA_O there is new data available Parallel port to transfer the data to the CED1Z_interface module Signal used to write data in the driver’s internal registers, data which will be sent to the ADAS3022ĭata bus, used to send new configuration words to the ADAS3022

Bits are used for data and are used as address. Register used to perform writes on the device under test. Register used to configure the base address of the memory location where the acquired data is to be writtenīit 0 is used to signal that the acquisition is completeīit 1 is used to signal that the internal memory buffer has been overflownīit 2 is used to signal that the user has performed a write of a read only register register Register used to configure the number of samples to be acquired when acquisition is started

#What to do if quartus ii can't pick up my usb blaster software#

Table 3 describes the registers of the Avalon peripheral:īit 1 is used to initiate software reset of the coreīit 2 is used to configure the Avalon write master core to write data to the same locationīit 3 is used to write data to the ADAS3022 evaluation board Used to select the register to be read from the ADAS3022EDZ board. Signal used by the CED1Z board to write data to the ADAS3022EDZ board Signal used by the CED1Z board to read data from the ADAS3022EDZ board Once the conversion is complete and the result is available in the output register, the BUSY output goes high Signal that indicates the status of the conversion. The ip subfolder contains the ADAS3022 SOPC componentĬontains the source files of the Nios2 SBT evaluation projectĬontains the script files used for data acquisitionīidirectional data bus used to write/read data to/from the ADAS3022EDZ board The src subfolder contains the HDL source files.Ĭontains the CED1Z Quartus evaluation project source files. The doc subfolder contains a brief documentation for the core.

#What to do if quartus ii can't pick up my usb blaster drivers#

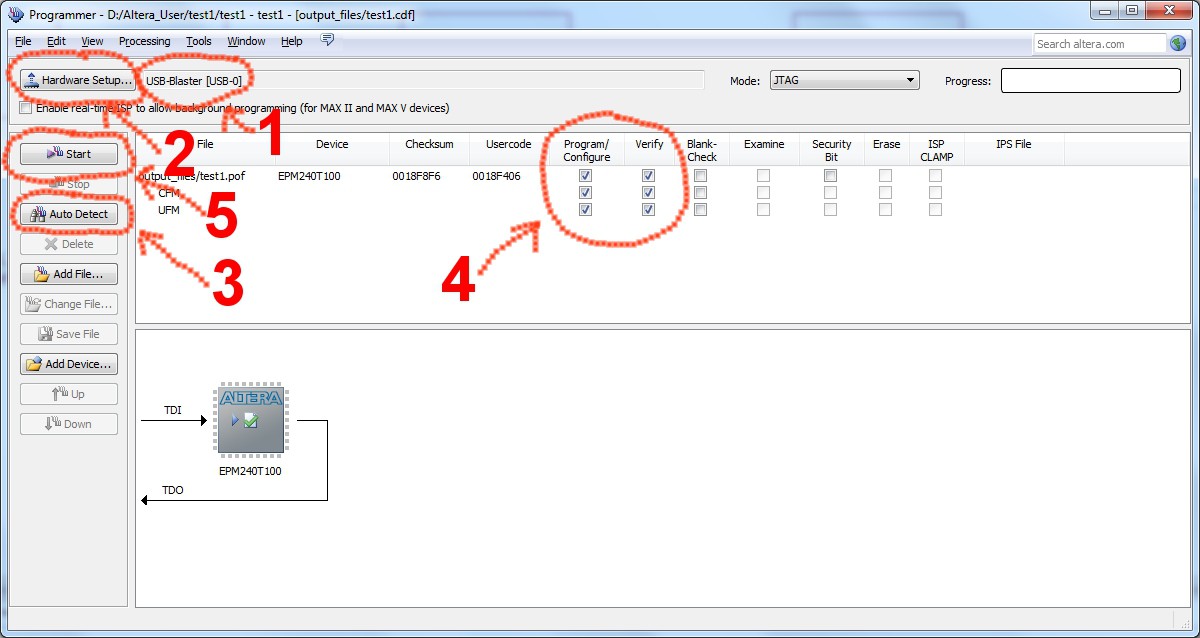

The ip subfolder contains the HDL core for connecting the evaluation board to the CED1Z board, the software drivers for HAL in /hdl/src/HAL and the ADAS3022 registers in /hdl/src/incĬontains the source files for the ADAS3022 core : New Nios2 applications can be created using the files from this folder. By executing the script program_fpga.bat the FPGA will be programmed with the evaluation project.

#What to do if quartus ii can't pick up my usb blaster driver#

The ADAS3022.v file contains the main ADC driver moduleĬontains all the files necessary to program the CED1Z board in order to evaluate the ADC. The EVAL-ADAS3022EDZ is an evaluation board for the ADAS3022 16-bit data acquisition system (DAS) with an aggregate throughput of 1 million samples per second (1MSPS).Ĭontains the reference project which is loaded on the EVAL-ADAS302圎DZ board. The ADAS3022 simplifies design challenges by eliminating signal buffering, level shifting, amplification/attenuation, common-mode rejection, settling time, or any of the other analog signal conditioning challenges while allowing smaller form factor, faster time to market, and lower costs. In addition, the device can accept the commonly used bipolar differential, bipolar single-ended, pseudo bipolar, or pseudo unipolar input signals, as shown in Table 1, thus enabling the use of almost any direct sensor interface. The ADAS3022 can resolve eight single-ended inputs or four fully differential inputs up to ☒4.576 V when using ☑5 V supplies. The device integrates an 8-channel, low leakage multiplexer a high-impedance programmable gain instrumentation amplifier (PGIA) stage with a high common-mode rejection a precision, low drift 4.096 V reference and buffer and a 16-bit charge-redistribution analog-to-digital converter (ADC) with successive approximation register (SAR) architecture. The ADAS3022 is a complete 16-bit, 1 MSPS, successive approximation–based analog-to-digital data acquisition system that is manufactured on Analog Devices, Inc., proprietary iCMOS® high voltage industrial process technology. It provides the necessary communications between the converter and the PC, programming or controlling the device, transmitting or receiving data over a USB link. The CED1Z board is intended for use in evaluation, demonstration and development of systems using Analog Devices precision converters. Below is presented a picture of the EVAL-ADAS3022EDZ Evaluation Board with the CED1 board. This document presents the steps to setup an environment for using the EVAL-ADAS3022EDZ evaluation board together with the EVAL-CED Converter Evaluation and Development (CED) Board, the Nios II Embedded Development Suite (EDS).